- 您现在的位置:买卖IC网 > Sheet目录1203 > COREU1PHY-AR (Microsemi SoC)IP MODULE COREU1PHY

�� �

�

�

�CoreU1PHY� –� UTOPIA� Level� 1� PHY� Interface�

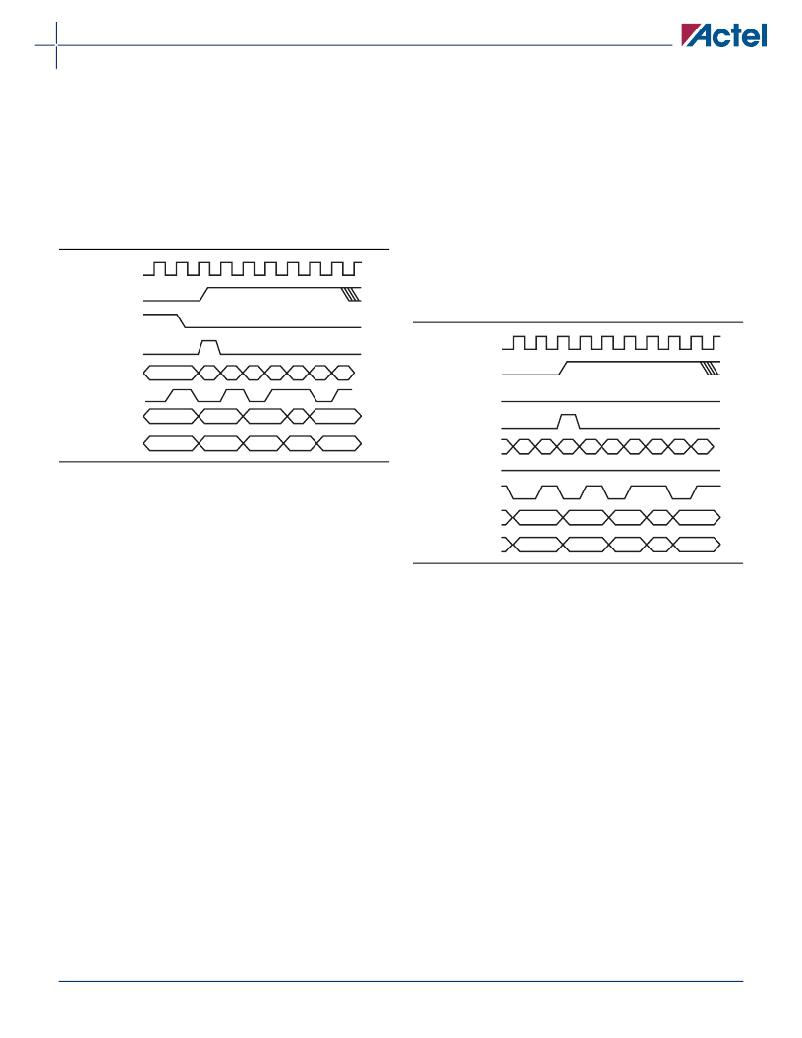

�Read� Interface� (egress)�

�When� r_avail� is� asserted� high� at� the� user� interface� and�

�the� u1_rx_en� signal� is� asserted� low� by� the� link-layer,� the�

�CoreU1PHY� will� begin� accepting� data� on� the� user�

�interface.� Once� a� cell� transfer� has� begun,� the� CoreU1PHY�

�will� transfer� 27� words� of� data� regardless� of� the� state� of�

�r_avail.� The� CoreU1PHY� asserts� r_buf_en� high,� expecting�

�to� accept� data� at� the� r_data� inputs� on� the� next� rising-�

��U1_rx_cl�

�U1_rx_cla�

�U1_rx_en�

�U1_rx_soc�

�accepted� on� the� following� rising� edge� of� u1_rx_clk,� and�

�the� r_adr� is� incremented.�

�Then� r_buf_en� is� de-asserted� for� one� clock� cycle� except�

�after� the� third� data� word� when� xlate� is� low� (53-byte�

�mode),� or� when� a� back-to-back� read� operation� is� needed�

�in� order� to� get� the� first� payload� byte� in� time.�

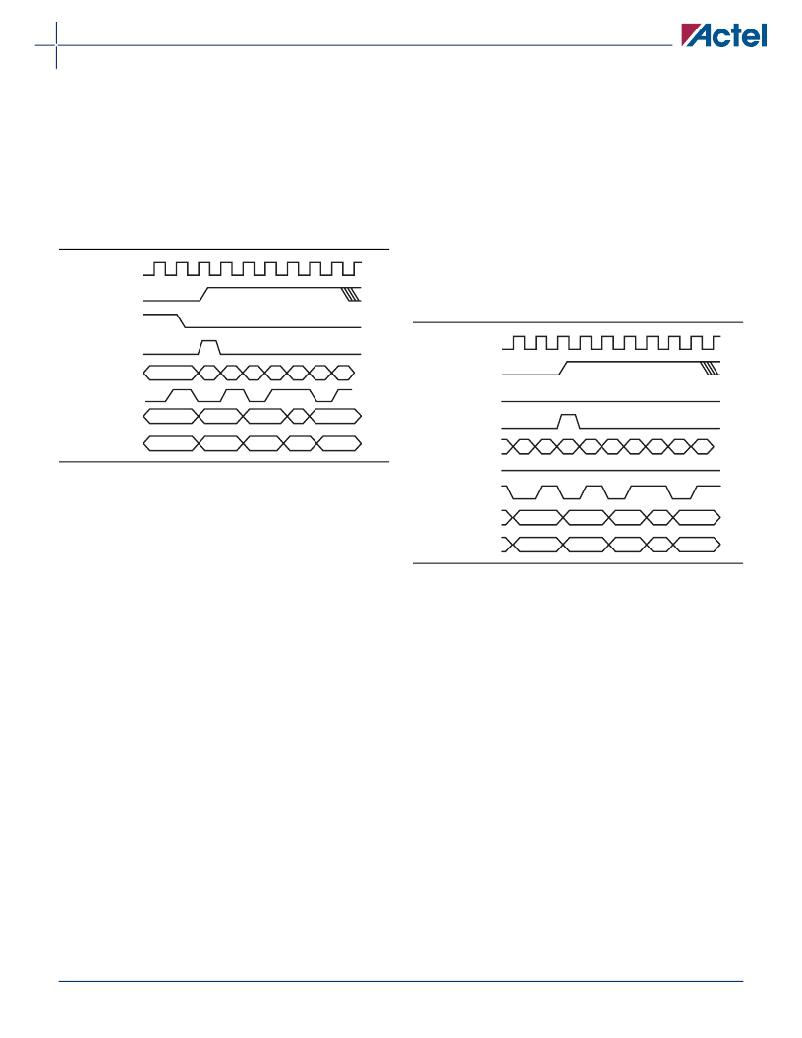

�The� cycle� is� repeated� until� r_adr� reaches� 1B� hex� and� the�

�last� two� bytes� of� the� ATM� cell� are� sent.� At� this� point,�

�r_adr� is� reset� to� 00� hex,� and� if� r_avail� indicates� that�

�another� cell� is� immediately� available,� and� u1_rx_en�

�remains� low,� the� CoreU1PHY� will� immediately� begin�

�sending� the� next� cell� as� shown� in� Figure� 11� .� Otherwise,�

�r_buf_en� remains� low� until� the� CoreU1PHY� begins� to�

�transmit� another� cell.�

�U1_rx_cl�

�U1_rx_data�

�XX�

�H1�

�H2�

�H3�

�H4�

�H5�

�P1�

�P2�

�U1_rx_clav�

�r_buf_en�

�U1_rx_en�

�r_adr�

�00�

�01�

�02�

�03�

�04�

�U1_rx_soc�

�r_data�

�XX�

�H1H2�

�H3H4�

�H5H6�

�P1P2�

�U1_rx_data�

�P47� P48�

�H1�

�H2�

�H3�

�H4�

�H5�

�P1�

�P2�

�Figure� 10� ?� Read� Interface� Cell� Transfer�

�The� CoreU1PHY� provides� r_adr� as� a� word� count� (00� to� 1B�

�R_avail�

�r_buf_en�

�hex)� and� increments� whenever� the� core� accepts� data� at�

�the� r_data� pins.� Since� the� CoreU1PHY� translates� from� 16-�

�bit� data� at� the� user� interface� to� 8-bit� data� at� the� UTOPIA�

�r_adr� 1B�

�r_data�

�00�

�XX�

�01�

�H1H2�

�02�

�H3H4�

�03�

�H5H6�

�04�

�P1P2�

�interface,� r_buf_en� is� asserted� for� one� clock� cycle,� data� is�

�Figure� 11� ?� Back-to-Back� Read� Cell� Transfer�

�v4.0�

�5�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

CORR-8BIT-XM-UT2

SITE LICENSE IP CORRELATOR XP

CP2-GSA-L

CONN SHIELD LOWER TYPE A 22

CP2-HSA110-1

CONN SHROUD CPCI 2MM TYPE A 22

CP2-HSC055-4

CONN SHROUD CPCI 2MM TYPE C 11

CP2-K3567-SR-F

COMPACT PCI - MISC

CP2105EK

KIT EVAL FOR CP2105

CP881

CONN BNC PLUG CRIMP RG-58

CP882

CONN BNC PLUG CRIMP RG-59,62

相关代理商/技术参数

COREU1PHY-EV

制造商:ACTEL 制造商全称:Actel Corporation 功能描述:CoreU1PHY - UTOPIA Level 1 PHY Interface

COREU1PHY-SN

制造商:ACTEL 制造商全称:Actel Corporation 功能描述:CoreU1PHY - UTOPIA Level 1 PHY Interface

COREU1PHY-SR

制造商:ACTEL 制造商全称:Actel Corporation 功能描述:CoreU1PHY - UTOPIA Level 1 PHY Interface

COREU1PHY-UR

制造商:ACTEL 制造商全称:Actel Corporation 功能描述:CoreU1PHY - UTOPIA Level 1 PHY Interface

COREU1PHY-XX

制造商:ACTEL 制造商全称:Actel Corporation 功能描述:CoreU1PHY - UTOPIA Level 1 PHY Interface

COREWARE

制造商:未知厂家 制造商全称:未知厂家 功能描述:CoreWare Merlin2 Fibre Channel core family

CORL-8P

功能描述:Connector 制造商:hirose electric co ltd 系列:* 零件状态:过期 标准包装:1

CORL-8S

功能描述:Connector 制造商:hirose electric co ltd 系列:* 零件状态:过期 标准包装:1